As a market leader in microcontrollers (MCUs) and microprocessors (MPUs), Renesas Electronics strives to anticipate customer design needs and address their challenges before they become costly pain points. This is true of our Renesas 32-bit and 64-bit proprietary core families, our broad Arm core portfolio, and extends to our low-power processes. In that spirit, we have put our support behind the next inflection in processor design – the RISC-V open ISA (instruction set architecture).

According to a new report from analyst firm BCC Research, RISC-V cores generated more than $445 million in 2021. The sector is projected to see a CAGR (compound annual growth rate) of more than 33 percent between 2022 and 2027 when it will reach $2.7 billion, driven by applications like industrial Internet of Things security, connected autonomous vehicles and high-performance computing.

A principal reason for the expected uptake is the widespread interest RISC-V is generating by removing the need for proprietary intellectual property licenses. As the RISC-V International consortium aptly describes it, RISC-V working groups do “all technical work visibly in the open,” with all archives available to the public. Just as importantly, all work carried out is considered to be community property, meaning that member companies have unfettered access to the RISC-V ISA upon which they are free to port software, design hardware, and develop new applications – at no charge.

RISC-V also lends itself to tighter code development than some proprietary processor core alternatives, which allows designers to customize their instructions and extensions. This encourages them to differentiate their products by improving software performance and power efficiency, which in some cases, allows design engineers to seamlessly migrate from 16-bit to 32-bit MCU architectures.

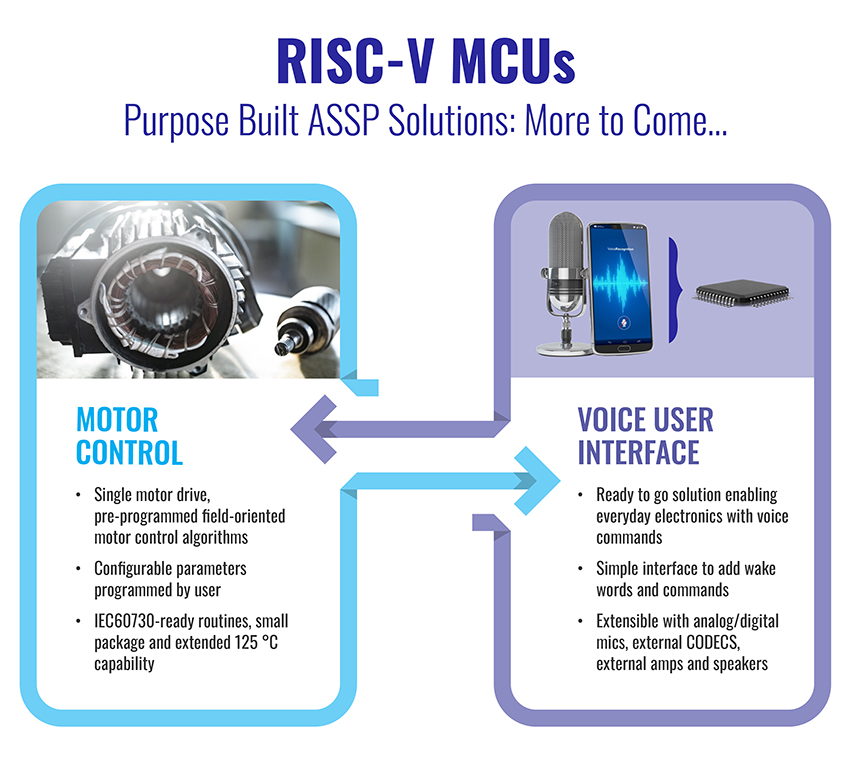

As we showed in September 2022, Renesas entered the RISC-V market with a 32-bit ASSP (application-specific standard product) optimized for advanced motor control systems. Working alongside our ecosystem partners, we enabled a complete, production-ready motor control solution that includes 32-MHz performance and all accompanying memory and analog designs to build a turnkey motor control solution, including specialized software. We expect to follow suit shortly with an ASSP optimized for voice-controlled human-machine interface systems.

Expanding Access to the Processor Ecosystem

To support our large MCU/MPU customer base with best-fit solutions, there are four development paths we typically see designers consider before deciding which direction to take. The first is to license all hardware, software and support tools, recognizing that the licensee will pay a premium for restricted access to proprietary technology. The second is to leverage the open-source RISC-V ISA and pursue an early market entry by partnering with independent design houses to leverage their pre-existing software and hardware implementation expertise. The third is to develop their own RISC-V cores in house, and the final option is to embrace established RISC-V collaboration platforms that enable them to share information with the open-hardware community.

Our Renesas RISC-V ASSPs, for example, leverage the third-party partner ecosystem, which allows us early access to the entire development chain – from algorithms, application software and evaluation tools – all while leveraging existing and proven 32-bit RISC-V CPU cores.

That is likely one thing that sets Renesas apart from other processor providers. Renesas has rich experience in the MCU/MPU market, including CPU architecture design. In addition, our comprehensive MCU/MPU ecosystem means we can develop commercially viable solutions that accommodate any options our customers choose – and even help guide them toward the markets and customers that best meet their design, applications and business needs.

As an active member of the RISC-V International consortium, we see our role as helping identify more opportunities for collaboration with other ecosystem partners. Think of us as a RISC-V champion, clearinghouse and matchmaker all rolled into one.